# ATC 5201 v06B

This is a connected intersection-ready Advanced Transportation Controller (ATC) Standard family developed by AASHTO, ITE, and NEMA

November 10, 2022

Advanced Transportation Controller (ATC) v06B.01

(Working Group Draft)

Supported/Sponsored By: The United States Department of Transportation (USDOT)

### Foreword

The Advanced Transportation Controller Standard (ATC Standard) is one of the four standards of the ATC family of standards. The ATC Standard provides a powerful, on-street, computing platform for numerous ITS applications intersection control, ramp metering, data collection, safety, security, and other applications. It uses a transportation controller architecture where the computational components of the controller reside on a single small printed circuit board (PCB), called the "Engine Board," with standardized connectors and pinout. It is made up of a central processing unit (CPU), Linux operating system (O/S), memory, external and internal interfaces, and other associated hardware necessary to create an embedded transportation computing platform. The Engine Board plugs into a "Host Module" which supplies power and physical connection to the input/output (I/O) facilities of the controller. While the interface to the Engine Board is completely specified, the Host Module may be of various shapes and sizes to accommodate innumerable transportation controller designs and cabinet architectures. The ATC Standard works together with the Application Programming Interface (API) Standard to allow application programs to share the resources of the controller and the transportation field cabinet system.

More information on this standard effort can be found on the ITE website.

The Standards Development Organizations (SDOs) supporting this standard include the following:

## ITE

Siva Narla, <u>snarla@ite.org</u> Tatiana Richey, <u>trichey@ite.org</u> Nicola Tavares, <u>standards@ite.org</u>

## AASHTO

Venkat Nallamothu, <u>vnallamothu@aashto.org</u> Gummada Murthy, <u>gmurthy@aashto.org</u>

### NEMA

Brian Doherty, <u>brian.doherty@nema.org</u> Steve Griffith, <u>steve.griffith@nema.org</u>

# Controller Working Group Co-chairs

John Thai, City of Anaheim (Public Sector) Jim Rose, Econolite (Private Sector)

# Controller Working Group (WG) Members

Ralph Boaz, Pillar Consulting, Inc. George Chen, LADOT Mike Gallagher, Q-Free Robin Harrison, Oriux Herasmo Iniguez, McCain Mohammad Iraki, CalTrans Dave Miller, Yunex Traffic Clyde Neel, Cubic Robert Rausch, TransCore Peter Skewers, Minnesota DOT Mohamed Talas, NYCDOT Derek Vollmer, Florida DOT April Wire, Maricopa County, AZ DOT

# **ATC Joint Committee Members**

Doug Crawford, Q-Free Alan Davis, Georgia DOT Kleinjan Deetlefs, Applied Information Steve Gault, Pennsylvania DOT Matt Luker, Utah DOT Dave Miller, Yunex Traffic Robert Rausch, TransCore Edward Seymour, Texas Transportation Institute Doug Spencer, ODOT Mohamed Talas, New York City DOT John Thai, City of Anaheim Andy Dowie, Eberle Design Inc. Jon Wyatt, Parsons Derek Vollmer, Florida DOT

# Subject Matter Experts (SMEs)

Ralph Boaz, Pillar Consulting, Inc. James Kinnard, Adaptive Solutions, Inc.

# **Copyright Notice**

#### NOTICE

© 2022 by the American Association of State Highway and Transportation Officials (AASHTO), the Institute of Transportation Engineers (ITE), and the National Electrical Manufacturers Association (NEMA).

These materials are delivered "AS IS" without any warranties as to their use or performance.

NEMA, AASHTO, ITE AND THEIR SUPPLIERS DO NOT WARRANT THE PERFORMANCE OR RESULTS YOU MAY OBTAIN BY USING THESE MATERIALS. NEMA, AASHTO, ITE AND THEIR SUPPLIERS MAKE NO WARRANTIES, EXPRESSED OR IMPLIED, AS TO NON-INFRINGEMENT OF THIRD-PARTY RIGHTS, MERCHANTABILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL NEMA, AASHTO, ITE OR THEIR SUPPLIERS BE LIABLE TO YOU OR ANY THIRD PARTY FOR ANY CLAIM OR FOR ANY CONSEQUENTIAL, INCIDENTAL, OR SPECIAL DAMAGES, INCLUDING ANY LOST PROFITS OR LOST SAVINGS ARISING FROM YOUR REPRODUCTION OR USE OF THESE MATERIALS, EVEN IF A NEMA, AASHTO, OR ITE REPRESENTATIVE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Some states or jurisdictions do not allow the exclusion or limitation of incidental, consequential, or special damages, or exclusion of implied warranties, so the above limitations may not apply to you.

Use of these materials does not constitute an endorsement or affiliation by or between NEMA, AASHTO, or ITE, and you, your company, or your products and services.

If you are not willing to accept the foregoing restrictions, you should immediately return these materials.

### **Content and Liability Disclaimer**

The information in this publication was considered technically sound by the consensus of persons engaged in the development and approval of the document at the time it was developed. Consensus does not necessarily mean that there is unanimous agreement among every person participating in the development of this document. NEMA, AASHTO and ITE standards and guideline publications, of which the document contained herein is one, are developed through a voluntary consensus standards development process. This process brings together volunteers and/or seeks out the views of persons who have an interest in the topic covered by this publication. While NEMA, AASHTO and ITE administer the process and establish rules to promote fairness in the development of consensus, they do not write the document and they do not independently test, evaluate, or verify the accuracy or completeness of any information or the soundness of any judgments contained in their standards and guideline publications. NEMA, AASHTO or ITE disclaim liability for any personal injury, property, or other damages of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly, or indirectly resulting from the publication, use of, application, or reliance on this document. NEMA, AASHTO and ITE disclaim and make no guaranty or warranty, express or implied, as to the accuracy or completeness of any information published herein and disclaims and makes no warranty that the information in this document will fulfill any of your particular purposes or needs. NEMA, AASHTO and ITE do not undertake to guarantee the performance of any individual manufacturer or seller's products or services by virtue of this standard or guide.

In publishing and making this document available, NEMA, AASHTO or ITE are not undertaking to render professional or other services for or on behalf of any person or entity, nor are they undertaking to perform any duty owed by any person or entity to someone else. Anyone using this document should rely on his or her own independent judgment or, as appropriate, seek the advice of a competent professional in determining the exercise of reasonable care in any given circumstances. Information and other standards on the topic covered by this publication may be available from other sources, which the user may wish to consult for additional views or information not covered by this publication.

NEMA, AASHTO and ITE have no power, nor do they undertake to police or enforce compliance with the contents of this document. NEMA, AASHTO and ITE do not certify, test, or inspect products, designs, or installations for safety or health purposes. Any certification or other statement of compliance with any health or safety–related information in this document shall not be attributable to NEMA, AASHTO or ITE and is solely the responsibility of the certifier or maker of the statement.

### Additional Contributors and Reviewers

In addition to the SDOS, Co-Chairs, WG Members and SMEs, there were many others that contributed to the development of this standard and their input and assistance was critical to the final product. The following list includes those volunteers and others who gave their time to help both the consultant and the committee ensure that the resulting standard met their needs. The following is a more complete list of those who volunteered their time and travel to contribute to the input and review during the development of this standard: <u>The Standards Discussion Groups on ITE Community</u> (ATC Community).

### **CHANGE HISTORY**

| DATE       | VERSION               | NOTE                                                                                                          |

|------------|-----------------------|---------------------------------------------------------------------------------------------------------------|

| 06/26/2006 | Version 5.2b          | Release version.                                                                                              |

| 07/14/2011 | Version 6.0a          | Draft for Working Group review. Includes disposition of                                                       |

|            |                       | working group comments submitted for ATC Standard v5.2b.                                                      |

| 06/08/2012 | Versions 06.01 –06.09 | Technical updates and document reformatting.                                                                  |

| 07/30/2012 | Version 06.10         | User Comment Draft.                                                                                           |

| 06/15/2015 | Version 06.20         | Working Group Draft following the incorporation of changes                                                    |

|            |                       | based on the adjudication comments by the ATC WG on UCD                                                       |

|            |                       | ATC 5201 Standard v06.10.                                                                                     |

| 08/10/2015 | Version 06.21         | Second Working Group Draft to address comments received                                                       |

|            |                       | regarding first Working Group Draft v06.20.                                                                   |

| 08/24/2015 | Version 06.22         | Third Working Group Draft to address comments received                                                        |

|            |                       | regarding Working Group Drafts v06.20 and v06.21.                                                             |

| 08/31/2015 | Version 06.23         | Proposed Recommended Standard (pRS); addresses                                                                |

|            |                       | comments received regarding Working Group Drafts v06.20,                                                      |

|            |                       | v06.21 and v06.22.                                                                                            |

| 10/04/2015 | Version 06.24         | Recommended Standard accepted by the ATC Joint                                                                |

|            |                       | Committee.                                                                                                    |

| 01/12/2018 | Version 06.25         | Joint Standard of AASHTO, ITE and NEMA.                                                                       |

| 09/30/2017 | Version 06.30         | Working Group Draft (WGD) to addressing comments                                                              |

|            |                       | received regarding Recommended Standard v06.24. Note that                                                     |

|            |                       | the date of this WGD precedes that of Version 06.25 due to a                                                  |

|            |                       | delay in the approval process.                                                                                |

| 05/09/2018 | Version 06.31         | Proposed User Comment Draft (pUCD) sent to the ATC Joint                                                      |

|            |                       | Committee.                                                                                                    |

| 06/30/2018 | Version 06.32         | User Comment Draft (UCD). Administrative advancement of                                                       |

| 04/00/0040 |                       | the minor version number.                                                                                     |

| 04/30/2019 | Version 06.33         | Working Group Draft with comments on the UCD version                                                          |

|            |                       | adjudicated and addressed. Subsequently voted by the<br>Controller WG to send to the ATC Joint Committee as a |

|            |                       |                                                                                                               |

| 05/24/2019 | Version 06A.34        | Proposed Recommended Standard on 5/14/19.                                                                     |

| 05/24/2019 | Version 00A.34        | Proposed Recommended Standard (pRS) sent to the ATC Joint Committee for review. Editorial updates made after  |

|            |                       | Controller WG acceptance of v06.33 are included.                                                              |

|            |                       | Subsequently accepted by vote of the ATC JC as a                                                              |

|            |                       | Recommended Standard on 06/20/19.                                                                             |

| 09/03/2019 | Version 06A.35        | Editorial updates post ATC Joint Committee acceptance of                                                      |

| 00/00/2010 | Version 00A.00        | v06A.34.                                                                                                      |

| 01/10/2020 | Version 06A.36        | Recommended Standard sent to AASHTO, ITE and NEMA for                                                         |

| 01/10/2020 |                       | final ballot. Includes additional editorial updates.                                                          |

| 07/29/2020 | Version 06A.37        | ATC 5401 v06A (v06A.37). Joint Standard of AASHTO, ITE                                                        |

|            |                       | and NEMA. Minor editorial corrections and changes made for                                                    |

|            |                       | publication.                                                                                                  |

| 11/10/2022 | Version 06B.01        | Working Group Draft following the incorporation of changes                                                    |

| 1,10,2022  |                       | based on the adjudication of comments by the ATC WG on                                                        |

|            |                       | ATC 5201 Standard v06A.37.                                                                                    |

|            |                       |                                                                                                               |

### TABLE OF CONTENTS

| 1 | INTRODU   |                                                                        | 1  |

|---|-----------|------------------------------------------------------------------------|----|

|   | 1.1 Purp  | ose                                                                    | 1  |

|   | 1.2 Scop  | )e                                                                     | 1  |

|   | 1.2.1     | Procurement Guidance                                                   | 1  |

|   | 1.3 Defir | nitions, Acronyms, and Abbreviations                                   | 2  |

|   | 1.3.1     | Physical Units                                                         | 2  |

|   | 1.3.2     | Modifiers                                                              | 3  |

|   | 1.3.3     | Acronyms and Definitions                                               | 3  |

|   | 1.4 Refe  | rences                                                                 | 6  |

|   | 1.4.1     | Contact Information                                                    | 7  |

|   | 1.5 Over  | view                                                                   | 7  |

| 2 | OVERALL   | DESCRIPTION                                                            | 8  |

|   |           | uct Perspective                                                        |    |

|   | 2.2 Oper  | rational Environment                                                   | 11 |

|   | 2.3 Repr  | esentative Usage                                                       |    |

|   | 2.3.1     | Manage/Configure Controller Applications                               |    |

|   | 2.3.2     | Manage External Devices                                                |    |

|   | 2.3.3     | Facilitate Ease of Maintenance and Future Hardware/Software Updates    |    |

|   |           | es of Operation                                                        |    |

|   |           | ırity                                                                  |    |

| 3 |           | NAL REQUIREMENTS                                                       |    |

|   |           | age/Configure Controller Applications                                  |    |

|   | 3.1.1     | Install and Update Applications Software                               |    |

|   | 3.1.2     | Installing and Upgrading the Operating System Software                 |    |

|   | 3.1.3     | Maintain Clock/Calendar Function and Synchronize with External Sources |    |

|   | 3.1.4     | Configure and Verify Parameters                                        |    |

|   | 3.1.5     | Uploading/Downloading Data Block(s)                                    |    |

|   | 3.1.6     | Monitoring and Verifying Present Application Status                    |    |

|   | 3.1.7     | Allowing Operator Control of Application(s)                            |    |

|   | 3.1.8     | Facilitate the Retention of Data                                       |    |

|   | 3.1.9     | Holdup Power                                                           |    |

|   |           | age External Devices                                                   |    |

|   |           | itate Ease of Maintenance and Future Hardware/Software Updates         |    |

|   | 3.3.1     | Board Support Package (BSP)                                            |    |

|   | 3.3.2     | Provide a Platform that Allows for Hardware Upgrades                   |    |

|   | 3.3.3     | Facilitate Software Application Portability                            |    |

|   | 3.3.4     | Facilitate Diagnostic Capabilities                                     |    |

| 4 |           | OARD DETAILS                                                           |    |

|   |           | eral Information                                                       |    |

|   | 4.1.1     | Engine Board                                                           |    |

|   | 4.1.2     | Host Module                                                            |    |

|   |           | nanical and Physical                                                   |    |

|   | 4.2.1     | Board Dimensions and Mechanical Requirements                           | 25 |

|   | 4.2.2     | Connector Pinout and Signal Names                        | 27 |

|---|-----------|----------------------------------------------------------|----|

|   | 4.2.3     | Environmental Requirements                               | 29 |

|   | 4.3 On-E  | Board Resources                                          | 29 |

|   | 4.3.1     | Central Processing Unit                                  | 29 |

|   | 4.3.2     | Startup Considerations                                   | 29 |

|   | 4.3.3     | Memory                                                   | 30 |

|   | 4.3.4     | Real-Time Clock (RTC)                                    | 31 |

|   | 4.3.5     | ATC Board Support Package (BSP)                          | 32 |

|   | 4.4 Elect | rical Interface                                          | 33 |

|   | 4.4.1     | Power                                                    | 33 |

|   | 4.4.2     | Synchronization                                          | 34 |

|   | 4.4.3     | Serial Interface Ports                                   | 34 |

|   | 4.4.4     | Programming/Test Port                                    | 40 |

|   | 4.4.5     | Miscellaneous                                            | 41 |

|   | 4.4.6     | SD Card                                                  | 41 |

| 5 | COMMUN    | CATION INTERFACE DETAILS                                 | 42 |

|   | 5.1 Gene  | eral Description                                         | 42 |

|   | 5.1.1     | Interchangeability Control                               |    |

|   | 5.1.2     | Communication Interface Slot Identification (deprecated) |    |

|   | 5.1.3     | Serial Port Identification                               | 43 |

|   | 5.2 Mech  | nanical Description                                      |    |

|   | 5.2.1     | Mechanical Outline Dimensions                            |    |

|   | 5.2.2     | ATC Communications Connector Mechanical Pin Assignments  |    |

|   | 5.2.3     | Standardized Legacy Field Connections                    |    |

|   | 5.3 Oper  | ational Description                                      |    |

|   | 5.3.1     | Interface to ATC                                         |    |

|   | 5.3.2     | Modulation and Demodulation                              |    |

|   |           | munications Interface Versions                           |    |

|   |           | Interface General Description                            |    |

|   | 5.5.1     | Minimum User Interface                                   |    |

|   | 5.5.2     | Optional User Interfaces                                 |    |

|   | 5.5.3     | User Interface Pin Connections                           |    |

|   | 5.5.4     | User Interface Operation                                 |    |

|   |           | er Supply General Description                            |    |

|   | 5.6.1     | "On/Off" Power Switch (optional)                         |    |

|   | 5.6.2     | LED DC Power Indicators (optional)                       |    |

|   | 5.6.3     | Service Voltage Over-Current Protection Device           |    |

|   | 5.6.4     | +5 VDC Standby Power                                     |    |

|   | 5.6.5     | Monitor Circuitry                                        |    |

|   | 5.6.6     | External Power Supply Requirements                       |    |

|   | 5.6.7     | Internal Power Supply Requirements                       |    |

|   | 5.7 Mech  | nanical and Physical General Description                 |    |

|   | 5.7.1     | Chassis                                                  |    |

| 6 | PARALLE   | L AND SERIAL I/O DETAILS                                 | 83 |

|   | 6.1 Ge  | neral Information                                                                                   | 83  |

|---|---------|-----------------------------------------------------------------------------------------------------|-----|

|   | 6.1.1   | Parallel Input / Output Overview                                                                    | 83  |

|   | 6.1.2   | Serial I/O Overview                                                                                 | 83  |

|   | 6.2 Pa  | rallel Input / Output (PI/O)                                                                        | 83  |

|   | 6.2.1   | Parallel Connection to Model 332 Cabinets                                                           | 83  |

|   | 6.2.2   | Parallel Connection to NEMA TS-1 or TS-2 Type 2 Cabinets                                            | 97  |

|   | 6.2.3   | Connection to NEMA TS-2 Type 1 Cabinets                                                             | 100 |

|   | 6.3 Se  | rial Input / Output                                                                                 | 101 |

|   | 6.4 Iso | lation Requirements                                                                                 | 103 |

|   | 6.4.1   | Engine Board Isolation                                                                              | 104 |

|   | 6.4.2   | Parallel I/O Isolation                                                                              | 104 |

|   | 6.4.3   | Serial I/O Isolation                                                                                | 104 |

|   | 6.5 Ele | ctrostatic Discharge Protection Requirements                                                        | 105 |

| 7 | ENVIRO  | NMENTAL AND TEST PROCEDURES                                                                         | 106 |

|   | 7.1 Ge  | neral                                                                                               | 106 |

|   | 7.1.1   | Engine Board Communication Loading Test                                                             | 107 |

|   | 7.1.2   | Timing Accuracy and Repeatability Test (TART)                                                       | 108 |

|   | 7.2 Ins | pection                                                                                             | 108 |

|   | 7.3 Te  | sting Certification                                                                                 | 108 |

|   | 7.4 De  | finitions of Design Acceptance Testing (DAT) and Production Testing                                 | 108 |

|   | 7.5 En  | vironmental and Operating Requirements                                                              | 108 |

|   | 7.5.1   | Voltage and Frequency                                                                               | 108 |

|   | 7.5.2   | Transients, Power Service (DAT)                                                                     | 109 |

|   | 7.5.3   | Nondestructive Transient Immunity (DAT)                                                             | 109 |

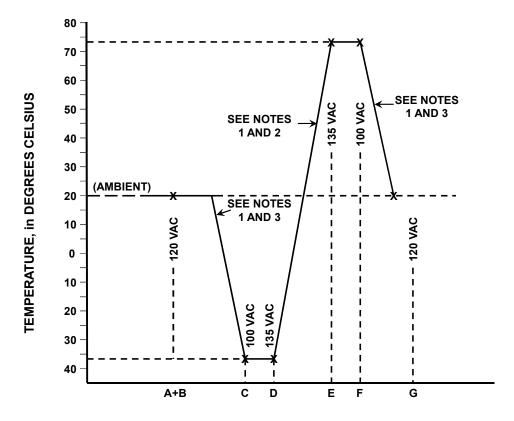

|   | 7.5.4   | Temperature and Humidity                                                                            | 109 |

|   |         | st Facilities                                                                                       |     |

|   | 7.7 Te  | st Procedures: Transients, Temperature, Voltage and Humidity                                        |     |

|   | 7.7.1   | Test A: Placement in Environmental Chamber and Check-Out of Hook-Up (DAT and<br>Production Testing) |     |

|   | 7.7.2   | Test B: Temperature Cycling and Applied Transient Tests (Power Service) (DAT)                       | 110 |

|   | 7.7.3   | Test C: Low-Temperature Low-Voltage Tests (DAT and Production Testing)                              | 111 |

|   | 7.7.4   | Test D: Low-Temperature High-Voltage Tests (DAT and Production Testing)                             | 111 |

|   | 7.7.5   | Test E: High-Temperature High-Voltage Tests (DAT and Production Testing)                            | 112 |

|   | 7.7.6   | Test F: High-Temperature Low-Voltage Tests (DAT and Production Testing)                             | 112 |

|   | 7.7.7   |                                                                                                     |     |

|   | 7.7.8   | Test H: Appraisal of Equipment Under Test                                                           | 112 |

|   |         | vration Test (DAT)                                                                                  |     |

|   | 7.9 Sh  | ock (Impact) Test (DAT)                                                                             | 112 |

|   | 7.9.1   | Purpose of Test                                                                                     | 112 |

|   |         | wer Interruption Test Procedures (DAT)                                                              |     |

|   |         | 1 Short Power Interruption                                                                          |     |

|   | 7.10.   | 2 Voltage Variation                                                                                 | 113 |

|   |         | 3 Rapid Power Interruption                                                                          |     |

|   |         | 4 Extended AC Line Synchronization Verification                                                     |     |

| 8 | PERFOR  | MANCE AND MATERIAL REQUIREMENTS                                                                     | 116 |

| 8.1 | Gene    | ral                                                  | . 116 |

|-----|---------|------------------------------------------------------|-------|

|     | 8.1.1   | Furnished Equipment                                  | . 116 |

|     | 8.1.2   | Edges                                                | . 116 |

|     | 8.1.3   | Hardware                                             | . 116 |

|     | 8.1.4   | Electrical Isolation and Equipment Grounding         | . 116 |

|     | 8.1.5   | Component Sources                                    | . 116 |

|     | 8.1.6   | Capacitors                                           | . 117 |

|     | 8.1.7   | Resistors                                            | . 117 |

|     | 8.1.8   | Semiconductors                                       | . 117 |

|     | 8.1.9   | Transformers and Inductors                           | . 118 |

|     | 8.1.10  | Single-Use Over-Current Protection Device            | . 118 |

|     | 8.1.11  | Switches                                             | . 118 |

|     | 8.1.12  | Wiring, Cabling, and Harnesses                       | . 118 |

|     | 8.1.13  | Indicators and Character Displays                    | . 119 |

|     | 8.1.14  | Connectors                                           | . 119 |

|     | 8.1.15  | PCB Design                                           | . 120 |

|     | 8.1.16  | Assemblies                                           | . 120 |

|     | 8.1.17  | Potentiometers                                       | . 120 |

|     | 8.1.18  | Batteries                                            | . 120 |

|     | 8.1.19  | Jumpers                                              | . 120 |

|     | 8.1.20  | Use of Fans                                          | . 120 |

|     | 8.1.21  | PCB Connectors                                       | . 121 |

|     | 8.1.22  | Tolerances                                           | . 121 |

| QU  | ALITY C | CONTROL                                              | . 122 |

| 9.1 | Comp    | ponents                                              | . 122 |

|     | 9.1.1   | Subassembly, Unit Or Module                          | . 122 |

|     | 9.1.2   | Predelivery Repair                                   | . 122 |

|     | 9.1.3   | Manufacturers' Quality Control Testing Certification | . 122 |

|     | 9.1.4   | Serial Numbers                                       | . 122 |

|     | 9.1.5   | Delivery                                             | . 122 |

9

### LIST OF FIGURES

### LIST OF TABLES

| Table 2-1. Some of the anticipated ATC applications                                                 | 12  |

|-----------------------------------------------------------------------------------------------------|-----|

| Table 4-1. Connector P1 Pinout and Signal Names                                                     | 28  |

| Table 4-2. Connector P2 Pinout and Signal Names.                                                    | 29  |

| Table 5-1. Minimum User Interface Components                                                        | 61  |

| Table 5-2. Optional User Interface Components                                                       | 62  |

| Table 5-3. Key Press Command-Response Codes                                                         | 64  |

| Table 5-4. Configuration Command Codes                                                              | 66  |

| Table 5-5. Inquiry Command-Response Codes                                                           | 68  |

| Table 5-6. Key Press Codes                                                                          | 69  |

| Table 5-7. AUX Switch Codes                                                                         | 70  |

| Table 5-8. Graphics Configuration Command Codes                                                     | 73  |

| Table 7-1. Ambient Temperature versus Relative Humidity At Barometric Pressures (29.92 Condensing). |     |

| Table A-1. Additional BSP Elements                                                                  | 124 |

|                                                                                                     |     |

### 1 INTRODUCTION

This section provides an introduction for this document. It includes sections on "Purpose," "Scope," "Definitions, Acronyms, and Abbreviations;" "References," and "Overview."

#### 1.1 Purpose

The Advanced Transportation Controller (ATC) standards are intended to provide an open architecture hardware and software platform that can support a wide variety of Intelligent Transportation Systems (ITS) applications including traffic management, safety, security, and other applications. The ATC standards are being developed and maintained under the direction of the ATC Joint Committee (JC) that is made up of representatives from the American Association of State Highway and Transportation Officials (AASHTO), the Institute of Transportation Engineers (ITE) and the National Electrical Manufacturers Association (NEMA).

This standard defines a transportation field device known as an ATC. It has been prepared by the Controller Working Group (WG), a technical subcommittee of the ATC JC. It establishes a common understanding of the specifications for an ATC for the following:

- a) Local, state, and federal transportation agencies who specify and use ATC equipment

- b) Manufacturers who produce ATC equipment

- c) Software developers who develop application programs for ATC equipment

- d) The public who benefit from the application programs that run on ATC equipment and who directly or indirectly pays for these products

### 1.2 Scope

The ATC Standard defines a minimum required functionality of hardware and software for ATCconforming transportation controllers. It includes a minimum processing capability, specifies a multi-tasking operating system, and a minimum set of user and communications interfaces. There is no limit on the use of technologies as long as these minimums are met. Its open architecture approach allows software to be purchased independently of the controller hardware and enables the ATC to be used for traditional traffic applications, advanced Intelligent Transportation Systems (ITS) or any other application requiring an on-street computing platform.

Other than the minimum physical interfaces, the ATC 5201 Standard is not specific on most mechanical aspects of the controller. This allows controllers to be built in conformance with this standard that will be compatible with all of the major transportation field cabinet systems and controllers available today including the Model 332 (family), NEMA TS 1, NEMA TS 2, Model 2070, ITS Cabinets and ATC Cabinets. See Section 1.4 for the referenced documents that describe the various field equipment standards and specifications.

### 1.2.1 **Procurement Guidance**

The ATC 5201 Standard requires the use of a minimum version of the Linux operating system and the inclusion of a Board Support Package (BSP). Agencies specifying the use of an ATC need to recognize that the ATC 5201 Standard does not prescribe a specific processor, processor clock speed, or a specific version of Linux; as a result, existing software may not be compatible with fully conformant ATCs from all vendors. Agencies should expect that the application software may need to be compiled and linked for the specific hardware, board support package, and version of Linux supplied since the object code may not be compatible for different processors. Further, some software may require modifications for specific hardware/platform [Linux and BSP] configurations. When purchasing ATC hardware separately from the application software, the agency may require software support services from their software vendor to verify compatibility, test the application, or to modify their application software for the specific platform and vendor chosen.

It is essential to understand that the ATC is a functional standard that identifies minimum requirements with a variety of options. This standard does not attempt to limit the features and future capabilities of the ATC. The intent is to define a transportation control platform that supports source code portability and interchangeability of application software programs. Agencies also need to recognize that it is inappropriate for a procurement specification to require the hardware vendor to ensure compatibility with a software package from another vendor (typically a competitor) or the agency itself, unless the source code is provided to the hardware vendor. Technology today advances rapidly, and it is not unusual for hardware obsolescence to outpace the life of the product in traffic control devices. The ATC 5201 Standard has been structured to allow for advances in technology (hardware and software) and to allow designs to change over time to adopt newer and better technology, which is sometimes necessitated by the obsolescence of key components. Such changes may require modification of application software programs.

### 1.3 Definitions, Acronyms, and Abbreviations

### 1.3.1 Physical Units

Wherever the following units are used, the intent and meaning shall be interpreted as follows:

| А   | Ampere                                   |

|-----|------------------------------------------|

| b   | bit                                      |

| bps | bits per second                          |

| В   | byte                                     |

| °C  | Degrees Celsius                          |

| dB  | Decibel                                  |

| dBa | Decibels above reference noise, adjusted |

| F   | Farad                                    |

| ft  | foot                                     |

| g   | gram                                     |

| G   | Earth gravitational constant             |

| Hz  | Hertz                                    |

| in  | inches                                   |

| J   | Joule                                    |

| m   | meter                                    |

| Ν   | Newton                                   |

| Ω   | Ohm                                      |

| S   | second                                   |

| V   | Volt                                     |

| W   | Watt                                     |

### 1.3.2 Modifiers

Wherever the following modifiers are used as a prefix to a physical unit, the intent and meaning shall be interpreted as follows:

- k kilo = 1000

- M Mega = 1 000 000

- m milli = 0.001

- μ micro = 0.000 001

- n nano = 0.000 000 001

- p pico = 0.000 000 000 001

### 1.3.3 Acronyms and Definitions

| AASHTO      | American Association of State Highway and Transportation Officials                                                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC<br>AC-   | Alternating Current                                                                                                                                                                                    |

| AC-<br>AC+  | 120 VAC, 60 Hz neutral (grounded return to the power source)                                                                                                                                           |

| AC+<br>ANSI | 120 VAC, 60 Hz line source (ungrounded)<br>American National Standard Institute                                                                                                                        |

| ANSI        |                                                                                                                                                                                                        |

|             | American Standard Code for Information Interchange                                                                                                                                                     |

| Assembly    | A complete machine, structure, or unit of a machine that was manufactured by fitting together parts and/or modules                                                                                     |

| ASTM        | American Society for Testing and Materials                                                                                                                                                             |

| ASYNC       | Asynchronous Serial Communications                                                                                                                                                                     |

| ATC         | Advanced Transportation Controller                                                                                                                                                                     |

| AWG         | American Wire Gage                                                                                                                                                                                     |

| BSP         | Board Support Package                                                                                                                                                                                  |

| Cabinet     | An outdoor enclosure generally housing the controller unit and associated equipment                                                                                                                    |

| Caltrans    | California Department of Transportation                                                                                                                                                                |

| CD          | Carrier Detect                                                                                                                                                                                         |

| Component   | Any electrical or electronic device                                                                                                                                                                    |

| CPU         | Central Processing Unit                                                                                                                                                                                |

| CTS         | Clear to send (data)                                                                                                                                                                                   |

| DAT         | Design Acceptance Testing                                                                                                                                                                              |

| DC          | Direct Current                                                                                                                                                                                         |

| DCD         | Data Carrier Detect (receive line signal detector)                                                                                                                                                     |

| DRAM        | Dynamic Random Access Memory                                                                                                                                                                           |

| EEPROM      | Electrically Erasable Programmable Read-Only Memory                                                                                                                                                    |

| EG          | Equipment Ground                                                                                                                                                                                       |

| EIA         | Electronic Industries Association                                                                                                                                                                      |

| EIA-694     | An EIA standard defining electrical characteristics only for an unbalanced digital interface with data signaling rates up to 512kbps (electrically compatible with EIA-232 but with higher data rates) |

| EL          | Electro-luminescent                                                                                                                                                                                    |

| EMI         | Electromagnetic Interference                                                                                                                                                                           |

| ENET        | Ethernet                                                                                                                                                                                               |

|             |                                                                                                                                                                                                        |

| EPROM       | Ultraviolet Erasable, Programmable, Read-Only Memory                                                                                                                                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Equal       | Connectors: conform to physical dimensions, contact material, plating, and method of connection.                                                                                                                                                              |

|             | Devices: conform to function, pin out, electrical and operating parameter requirements, access times and interface parameters of the specified device                                                                                                         |

| ETL         | Electrical Testing Laboratories, Inc.                                                                                                                                                                                                                         |

| FCU         | Field Controller Unit                                                                                                                                                                                                                                         |

| Firmware    | A computer program or software stored permanently in PROM, EPROM, ROM, or semi-permanently in EEPROM                                                                                                                                                          |

| FLASH       | Long-Term Non-Volatile Memory: a form of EEPROM that allows multiple<br>memory locations to be erased or written in one programming operation. It<br>is solid-state, permanent, and non-volatile memory typically having fast<br>access and read/write cycles |

| FPA         | Front Panel Assembly                                                                                                                                                                                                                                          |

| FSK         | Frequency Shift Keying                                                                                                                                                                                                                                        |

| GPS         | Global Positioning System                                                                                                                                                                                                                                     |

| HDLC        | High-level Data Link Control                                                                                                                                                                                                                                  |

| I/O         | Input/Output                                                                                                                                                                                                                                                  |

| IEEE        | Institute of Electrical and Electronics Engineers                                                                                                                                                                                                             |

| IP          | Internet Protocol                                                                                                                                                                                                                                             |

| ISO         | International Standards Organization                                                                                                                                                                                                                          |

| ITE         | Institute of Transportation Engineers                                                                                                                                                                                                                         |

| ITS         | Intelligent Transportation Systems (including standards approved by AASHTO/NEMA/ITE)                                                                                                                                                                          |

| Jumper      | A means of connecting/disconnecting two or more conductors by soldering/desoldering a conductive wire or by PCB post-jumper                                                                                                                                   |

| Keyed       | Means by which like connectors can be physically altered to prevent improper insertion                                                                                                                                                                        |

| LCD         | Liquid Crystal Display                                                                                                                                                                                                                                        |

| LED         | Light Emitting Diode                                                                                                                                                                                                                                          |

| LOGIC       | Negative logic convention (Ground True) state                                                                                                                                                                                                                 |

| logic-level | HCT or equivalent TTL – compatible voltage and fanout interface levels                                                                                                                                                                                        |

| lsb         | Least Significant Bit                                                                                                                                                                                                                                         |

| LSB         | Least Significant Byte                                                                                                                                                                                                                                        |

| MIPS        | Million Instructions Per Second                                                                                                                                                                                                                               |

| Model 2070  | A traffic control device that meets one of the California Department of Transportation (Caltrans) Transportation Electrical Equipment                                                                                                                         |

|             | Transportation (Caltrans) Transportation Electrical Equipment Specifications for Model 2070 traffic control devices.                                                                                                                                          |

| Module      | A functional unit that plugs into an assembly                                                                                                                                                                                                                 |

| msb         | Most Significant Bit                                                                                                                                                                                                                                          |

| MS          | Military Specification, Mil-Spec or Mil-Standard                                                                                                                                                                                                              |

| MSB         | Most Significant Byte                                                                                                                                                                                                                                         |

| N/A         | Not Applicable                                                                                                                                                                                                                                                |

| NA          | Presently Not Assigned. Cannot be used by the contractor for other                                                                                                                                                                                            |

|             | purposes.                                                                                                                                                                                                                                                     |

| NEMA   | National Electrical Manufacturer's Association                                                                               |

|--------|------------------------------------------------------------------------------------------------------------------------------|

| NETA   | InterNational Electrical Testing Association                                                                                 |

| NLSB   | Next Least Significant Byte                                                                                                  |

| NMSB   | Next Most Significant Byte                                                                                                   |

| NTCIP  | National Transportation Communication for ITS Protocol                                                                       |

| NTP    | Network Time Protocol                                                                                                        |

| NYSDOT | New York State Department of Transportation                                                                                  |

| O/S    | Operating System                                                                                                             |

|        | Standardized hardware interfaces in a module                                                                                 |

| OST    | Operating System Time                                                                                                        |

| PCB    | Printed Circuit Board                                                                                                        |

| RAM    | Random Access Memory                                                                                                         |

| RF     | Radio Frequency                                                                                                              |

| RMS    | Root mean square                                                                                                             |

| ROM    | Read only memory                                                                                                             |

| RTC    | Real Time Clock                                                                                                              |

| RTS    | Request to send (data)                                                                                                       |

| RX     | Abbreviation for "Receive" when used to describe communication signals.                                                      |

|        | Typically, a prefix for other character(s).                                                                                  |

| RXC    | Receive Clock                                                                                                                |

| RXD    | Receive Data                                                                                                                 |

| SDLC   | Synchronous Data Link Control                                                                                                |

| SP     | Serial Port                                                                                                                  |

| SPI    | Serial Peripheral Interface                                                                                                  |

| SRAM   | Static Random Access Memory                                                                                                  |

| SYNC   | Synchronous Serial Communications                                                                                            |

| TEES   | Transportation Electrical Equipment Specifications                                                                           |

| TMC    | Transportation Management Center                                                                                             |

| TOD    | Time Of Day Clock                                                                                                            |

| TTL    | Transistor-Transistor Logic                                                                                                  |

| ТХ     | Abbreviation for "Transmit" when used to describe communication signals.                                                     |

| TVO    | Typically a prefix for other character(s).                                                                                   |

| TXC    | Transmit Clock                                                                                                               |

| TXD    | Transmit Data                                                                                                                |

| UL     | Underwriter's Laboratories, Inc.                                                                                             |

| USB    | Universal Serial Bus                                                                                                         |

| VAC    | Volts Alternating Current                                                                                                    |

|        | Volts Direct Current                                                                                                         |

| WDT    | Watchdog Timer: A monitoring circuit, external to the device watched, which senses an Output Line from the device and reacts |

|        | שוווטו שבוושבש מוו טעוניעו בוווב ווטווו וווב עבעונד מווע ובמטוש                                                              |

### 1.4 References

Normative references contain provisions that, through reference in this text, constitute provisions of ATC 5201 v06. Other references in ATC 5201 v06 may provide a better understanding or provide additional information about certain features.

At the time of publication, the editions indicated below were valid. All standards are subject to revision, and parties to agreements based on ATC 5201 v06 are encouraged to investigate the possibility of applying the most recent editions of the standards listed.

"ATC 5201 v06, Advanced Transportation Controller (ATC) Standard Version 6," ATC JC, 29 July 2020. Available from the Institute of Transportation Engineers. <u>https://www.ite.org/technical-resources/standards/</u>

"ATC 5301 v02, Advanced Transportation Controller (ATC) Cabinet Standard Version 02," ATC JC, 18 March 2019. Available from the Institute of Transportation Engineers. <u>https://www.ite.org/technical-resources/standards/</u>

"ATC 5401 v02, Application Programming Interface (API) Standard for the Advanced Transportation Controller (ATC) Version 2," ATC JC, 15 September 2013. Available from the Institute of Transportation Engineers. <u>https://www.ite.org/technical-resources/standards/</u>

"Caltrans Transportation Electrical Equipment Specifications (TEES)," California Department of Transportation, 12 March 2009. Available from the California Department of Transportation. <u>http://www.dot.ca.gov/trafficops/tech/tees.html</u>

IEEE 802.3 Ethernet Specifications. Available from the Institute of Electrical and Electronics Engineers.

"Intelligent Transportation System (ITS) Standard Specification for Roadside Cabinets v01.02.17b," ATC JC, 16 November 2006. Available from the Institute of Transportation Engineers. <u>https://www.ite.org/technical-resources/standards/</u>

"ISO/IEC 13239:2002, Information technology -- Telecommunications and information exchange between systems -- High-level data link control (HDLC) procedures." Available from the International Organization for Standardization (ISO).

"ITU-T X.680 Information technology – Abstract Syntax Notation One (ASN.1): Specification of basic notation," International Telecommunication Union, August 2015. Available from the International Telecommunication Union (ITU).

"NEMA TS 1-1989, Traffic Control Systems," NEMA, 1989. Available from the National Electrical Manufacturers Association.

"NEMA TS 2-2016, Traffic Controller Assemblies with NTCIP Requirements Version 03.07," NEMA, 2016. Available from the National Electrical Manufacturers Association.

Universal Serial Bus (USB) Specifications. Available from USB Implementers Forum, Inc.

### 1.4.1 Contact Information

### 1.4.1.1 ISO/IEC Standards Information

ISO/IEC standards can be purchased on-line in electronic format or printed copy from:

Techstreet 6300 Interfirst Dr. Ann Arbor, MI 48108 (800) 699-9277 www.techstreet.com

### 1.4.1.2 NEMA Standards Information

NEMA standards can be purchased on-line in electronic format or printed copy from:

Techstreet 6300 Interfirst Dr. Ann Arbor, MI 48108 (800) 699-9277 www.techstreet.com

### 1.5 Overview

This standard is made up of 9 sections and three appendices. Section 1, "Introduction," provides an overview of the entire document. Section 2, "Overall Description," provides the background information and context necessary for the requirements. Section 3, "Functional Requirements" identifies the requirements of an ATC based on the "Representative Usage" described in Section 2. Sections 4-9 contain the detailed requirements and specifications for the ATC 5201 Standard.

### 2 OVERALL DESCRIPTION

This section provides an overall description for the ATC. It includes sections on "Product Perspective," "Operational Environment," "Representative Usage," "Modes of Operation" and "Security."

### 2.1 **Product Perspective**

Transportation controllers are environmentally-ruggedized computational devices used for onstreet field applications. They are designed to operate within a field cabinet system to carry out the functions of installed application programs. The most common of the field cabinet systems are those defined by the Model 332 (type) Specifications, the NEMA TS 1 Standard, the NEMA TS 2 Standard, the ITS Cabinet Standard and the ATC Cabinet Standard. Since the 1980's, the demand for more sophisticated transportation controllers has gone from simple intersection control to advanced Intelligent Transportation Systems (ITS) applications such as adaptive signal control, active traffic management and real-time vehicle-infrastructure systems. This has created a need for traffic controllers that are capable of performing a diversity of tasks, running concurrent application programs, and operating in high-speed communication networks.

There have been two general approaches to transportation controller architecture: 1) "open architecture" controllers where the hardware is so specified that third parties can develop application software for the device and 2) "closed architecture" controllers where the hardware and application software are produced and sold as a package. In open architecture controllers, the controller hardware is so specified that third party software developers can provide application programs for the device. In closed architecture controllers, the manufacturer provides both the hardware and the software for the device. One of the benefits of open architecture controllers are greater competition since any manufacturer can develop the hardware and third parties can provide application programs. One of the disadvantages is that, in the effort to provide portability, the technology used in the specification has been fixed (i.e., processor, commercial off-the-shelf operating systems, memory, etc.). This has led to underpowered equipment and early obsolescence. One of the benefits of closed architecture controllers has been their ability to take advantage of new technologies. Since the computational aspects of the hardware are not explicit, manufacturers have had the ability to apply innovative solutions more expeditiously in their transportation controllers. The drawbacks of the closed architecture approach are less competition and the inability to obtain application programs or custom software from third parties.

The ATC 5201 Standard has been developed to leverage the advantages of both architectural approaches. It specifies an open architecture computational capability intended to augment all of the current transportation equipment standards. The standard also has a built-in methodology for ATC units to grow with technology in order to provide for transportation controllers in the future. Some of the features of the ATC 5201 Standard are as follows:

- Works in Existing Cabinet Architectures. This is so users do not need to replace all of their field equipment and still benefit from transportation controllers built to the ATC 5201 Standard.

- Stated Minimum Processing Capability. This is necessary so that application developers (other than the original equipment manufacturer) understand what resources are guaranteed to be available for all ATC units.

- Standardized Method for Upgrading ATC Units. This mitigates issues with obsolescence and allows the standard to maintain relevancy for the future.

- Multi-Tasking Open Source Operating System. This is so software developers can write innovative application programs that can be made to operate on all ATC units and also

allows these application programs to run concurrently on the ATC. An additional benefit is that runtime license fees may not apply in these circumstances helping to reduce the cost to the user.

Various I/O Capabilities. This is to allow the ATC to perform internal cabinet system operations and external communications for whatever architecture or applications the ATC is designed for.

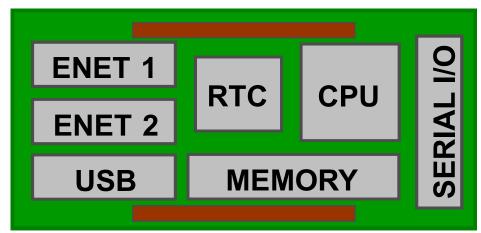

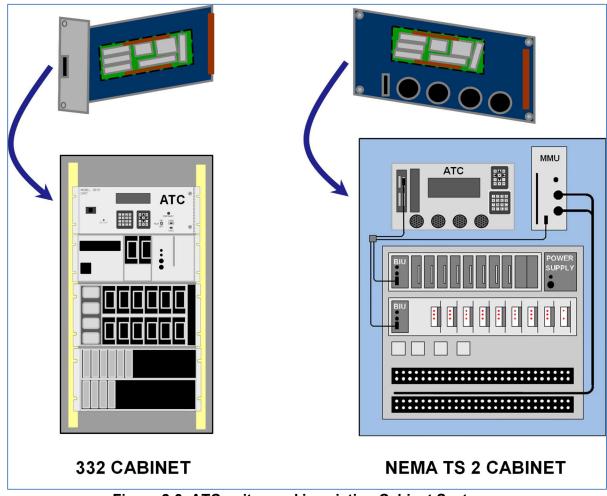

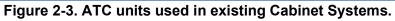

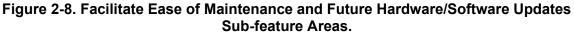

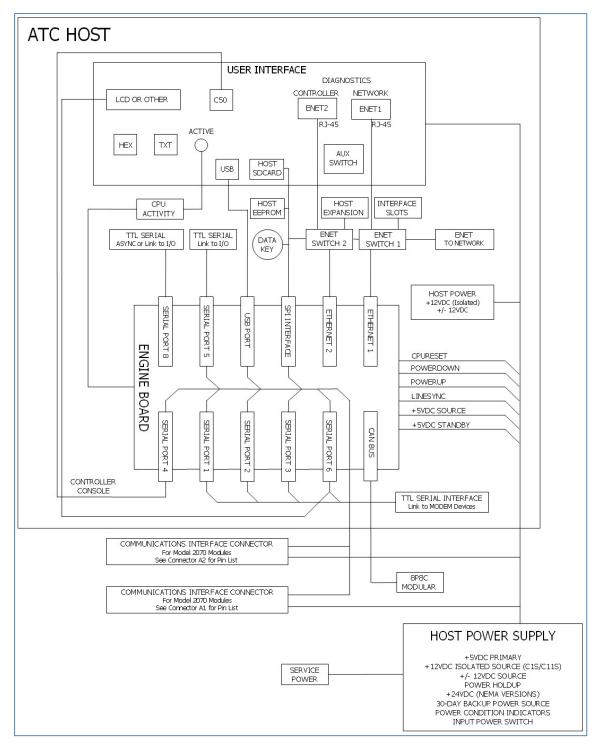

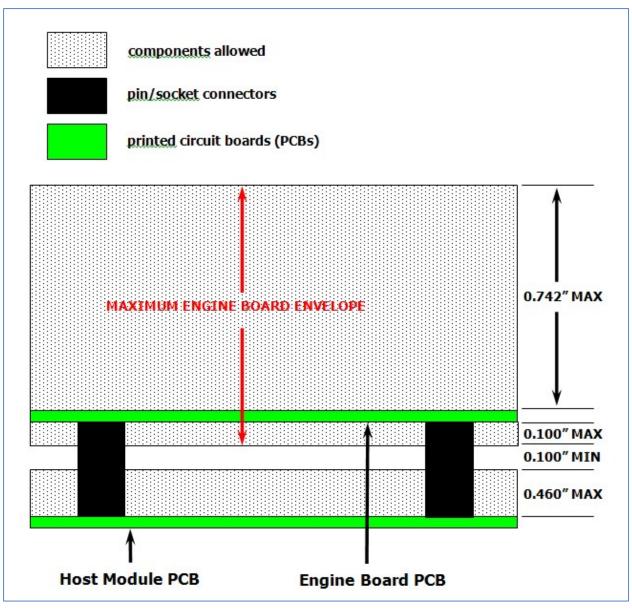

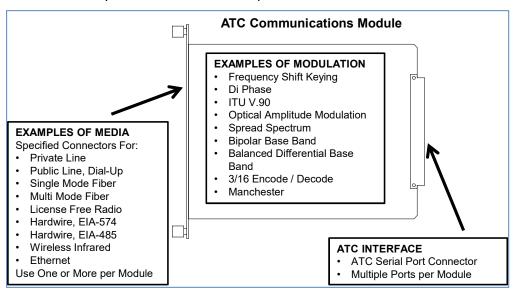

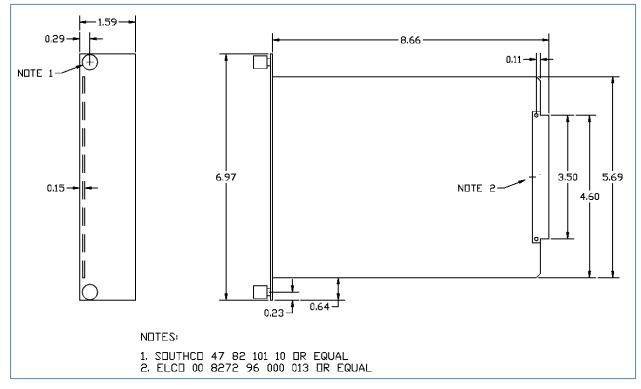

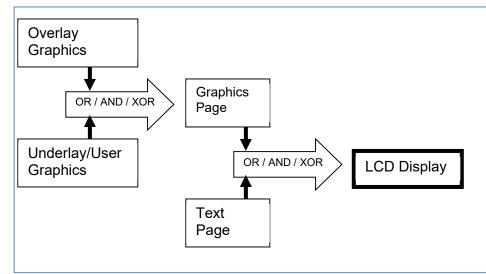

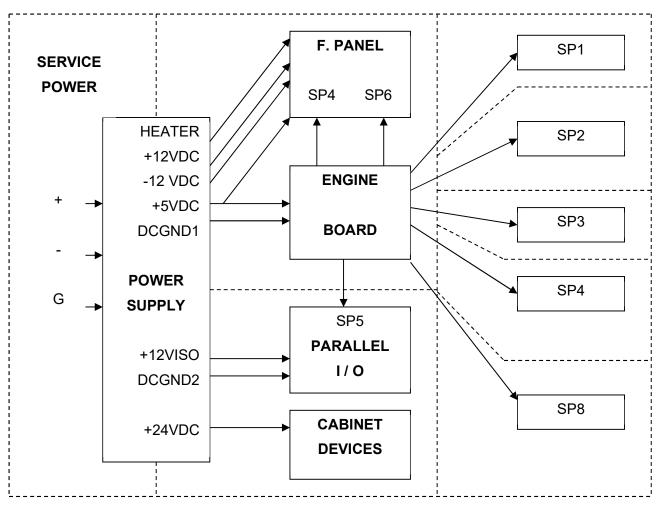

The ATC 5201 Standard uses a transportation controller architecture where the computational components of the controller reside on a single small printed circuit board (PCB), called the "Engine Board," with standardized connectors and pinout. It is made up of a central processing unit (CPU), Linux operating system (O/S), memory, external and internal interfaces, and other associated hardware necessary to create an embedded transportation computing platform (see Figure 2-1). The Engine Board plugs into a Host Module which supplies power and physical connection to the input/output (I/O) facilities of the controller. While the interface to the Engine Board is completely specified, the Host Module may be of various shapes and sizes to accommodate innumerable transportation controller designs and cabinet architectures. Figure 2-2 illustrates how the Engine Board and Host Module can be used in different types of transportation controllers. Figure 2-3 shows how a controller conformant with two different existing cabinet standards can utilize the architecture defined by the ATC Standard.

Guidance: In addition to the Linux operating system, software libraries are available to allow concurrently running application programs to share the resources of the ATC unit and its field cabinet system. These libraries and functionality are defined by the Application Programming Interface (API) Standard (see Section 1.4).

Guidance: The inclusion of an Engine Board in a transportation controller is not sufficient for said controller to be considered conformant to the ATC 5201 Standard. All other elements of the standard must also be satisfied.

Figure 2-1. Block diagram of the ATC Engine Board.

Figure 2-2. ATC Engine Board used in Host Modules for different types of transportation controllers.

### 2.2 **Operational Environment**

Typically, an operator interfaces to an ATC through one of the following three mechanisms:

- Remote computer this type of operation configures and manages ITS applications from a computer located at a traffic management location, such as a Transportation Management Center (TMC) or from a field located computer such as a traffic signal field master controller.

- Local computer this type of operation performs the same functions as a central computer does, but uses a portable interface device (e.g., laptop, etc.) connected directly to a port of the ATC.

- Locally this type of operation uses the front panel or portable interface devices (e.g., keyboard, displays, switches) at the ATC to perform the functions of configuring and managing the ITS applications.

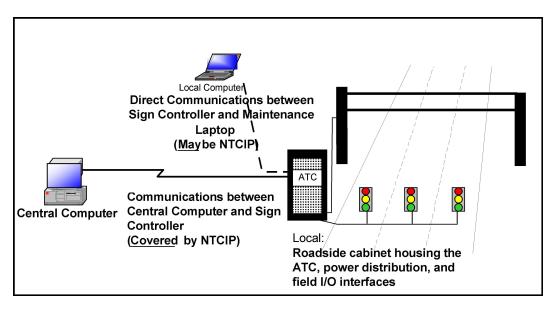

The connection between the central computer and the ATC runs over a communications network. This can be either hard-wired (cables) or wireless. The network interface at the ATC can be either a serial communications port or Ethernet port. Figure 2-4 depicts the physical architecture of the key components related to a typical ATC-based system run from a central location.

Figure 2-4. View of a Typical ATC System Environment.

The ATC is enclosed in a field-located cabinet. The ATC connects to other cabinet-located input/output devices (i.e., load switches, detector sensors, etc.) through serial and/or parallel connections. Cabinet input/output devices, in turn, connect to field-located elements (i.e., signal head, dynamic message sign, sensors, etc.).

In practice, there are additional components in a field-located cabinet which support the system including power distribution equipment, monitoring devices and terminal facilities. The exact device interfaces and cabinet configuration depends on the particular ITS application and type of equipment being deployed.

### 2.3 Representative Usage

As previously indicated, the functionality of a deployed ATC will depend on the applications software loaded into it. Some of the anticipated applications to be hosted on the ATC are listed in Table 2-1.

| Traffic Signal                      |

|-------------------------------------|

| Traffic Surveillance                |

| Lane Use Signals                    |

| Communications                      |

| Field Masters                       |

| Ramp Meter                          |

| Variable/Dynamic Message Signs      |

| General ITS Beacons                 |

| CCTV Cameras                        |

| Highway Rail Intersections          |

| Speed Monitoring                    |

| Incident Management                 |

| Highway Advisory Radio              |

| Freeway Lane Control                |

| High Occupancy Vehicle Systems      |

| Access Control                      |

| Roadway Weather Information Systems |

| Irrigation Control                  |

Table 2-1. Some of the anticipated ATC applications.

Due to its general purpose nature, an ATC may be used for future ITS applications that are not currently anticipated. These expanded functions may, over time, expand the operational user needs for an ATC. Nonetheless, a number of basic operational usage scenarios can be discerned from present day applications.

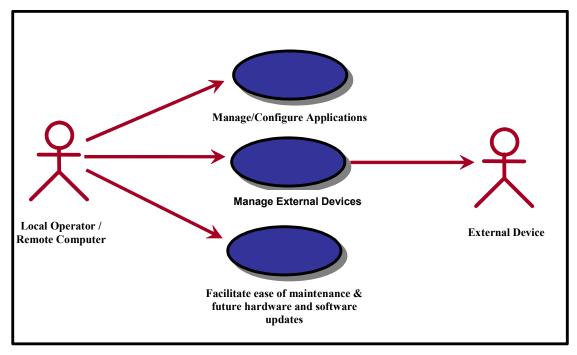

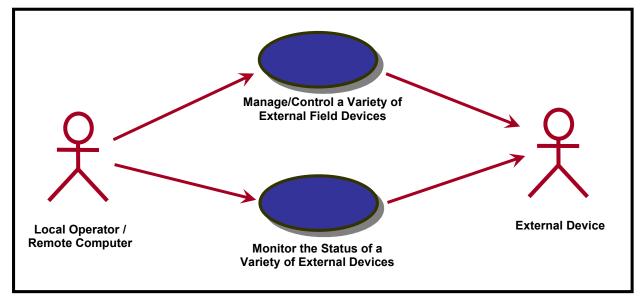

This section identifies and describes some of the most common "use cases" to be supported by the ATC and its applications software. Figure 2-5 provides a top-level view of the operational features offered by a typical ITS application using an ATC. The definition of each feature is provided after the presentation of the diagram. The features in this diagram are subdivided into more detailed features in the text below. For these use cases, a more detailed use case feature diagram is presented along with corresponding definitions. Section 3 then uses these definitions to organize and define the various functional requirements of an ATC.

### Figure 2-5. Main Maintenance / Support Diagram.

The generalized operational features of an ATC can be categorized into the following three major areas:

- Manage/Configure Applications

- Manage External Devices

- Facilitate Ease of Maintenance and Future Hardware/Software Updates

The maintenance and support function includes features for maintenance and update/enhancement of the controller unit's hardware and/or software.

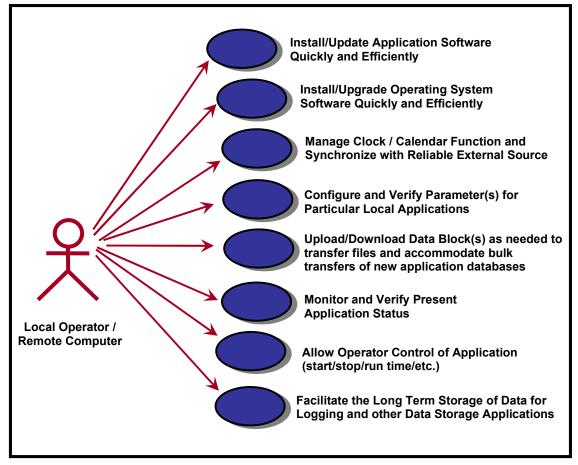

### 2.3.1 Manage/Configure Controller Applications

The various sub-features for managing and configuring software applications are shown in the following figure. The subsequent sections detail these sub-features.

Figure 2-6. Manage/Configure Applications' Sub-feature Areas.

### 2.3.1.1 Install/Update Applications Software Quickly and Efficiently

This feature allows the local operator to install or update the application software resident on the ATC. With Standard Operating Policies and appropriate safety precautions in place, a User may also permit a remote computer to install or update the application software resident on the ATC.

### 2.3.1.2 Install/Upgrade O/S Quickly and Efficiently

This feature allows the local operator to install or update the O/S resident on the ATC. With Standard Operating Policies and appropriate safety precautions in place, a User may also allow remote upgrade capability as an optional feature.

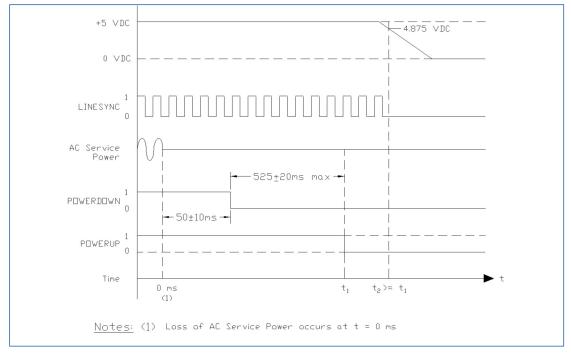

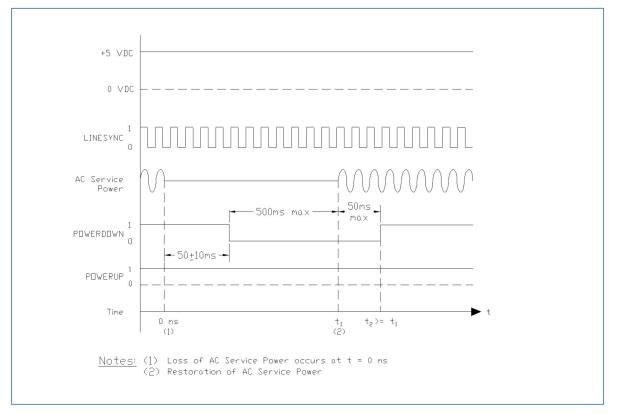

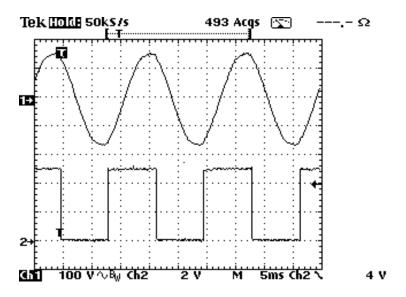

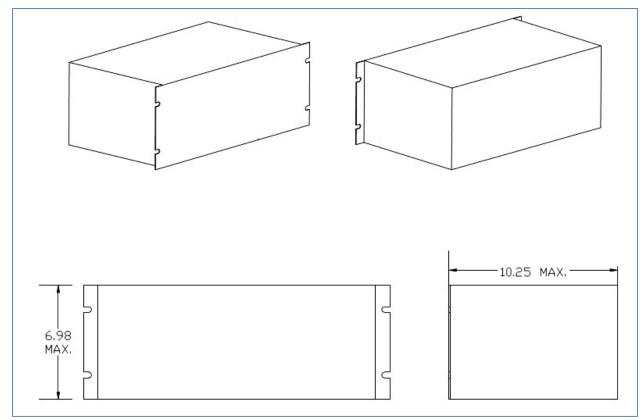

# 2.3.1.3 Manage Clock / Calendar Function and Synchronize with Reliable External Source